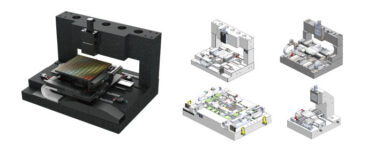

パナソニック電工は、実装面積4・6平方ミリメートルを実現し、プリント配線板における部品実装面積のさらなる縮小化ニーズを実現したPhotoMOSリレー「VSSOPタイプ」=写真=を発売した。オープン価格。11年度販売目標は120万個。

電子機器の小型化・高機能化に伴い、リレーをはじめ電子部品は実装面積の低減やさらなる電気的特性の良化が求められている。PhotoMOSリレーは入力側にLED、出力側に光電素子とMOSFETを採用し、光によって信号の伝達を行う半導体リレー。

同社は、小型半導体リレーとして「SSOPタイプ」(実装面積11・8平方ミリメートル)、「SONタイプ」(同6・5平方ミリメートル)を発売、好評を得ている。

VSSOPタイプは、SSOPタイプと比較し61%の実装面積削減を実現。同社のPhotoMOSリレーでは最小の同面積4・6平方ミリメートル(長さ2・1ミリメートル×幅2・2ミリメートル)を実現。高密度実装が求められる計測機器など、機器設計の自由度を高める。

高周波特性は、インサーションロス50Ω~10GHzで3dB以内。さらに、高周波通過特性の指標として、値が小さいほど信号の歪みが抑えられて良いとされるERT(Equivalent

Rise

Time)は、30Pa(平均)で、SONタイプと比較し約40%の良化を図った。

新構造設計により、高周波信号への対応が可能となり、特に半導体テスタの高速化、多ピン化に貢献している。

電気的特性は、低C×R、オン抵抗0・8Ω(平均)、出力端子間容量は14pF(同)。

オートメーション新聞は、1976年の発行開始以来、45年超にわたって製造業界で働く人々を応援してきたものづくり業界専門メディアです。工場や製造現場、生産設備におけるFAや自動化、ロボットや制御技術・製品のトピックスを中心に、IoTやスマートファクトリー、製造業DX等に関する情報を発信しています。新聞とPDF電子版は月3回の発行、WEBとTwitterは随時更新しています。

オートメーション新聞は、1976年の発行開始以来、45年超にわたって製造業界で働く人々を応援してきたものづくり業界専門メディアです。工場や製造現場、生産設備におけるFAや自動化、ロボットや制御技術・製品のトピックスを中心に、IoTやスマートファクトリー、製造業DX等に関する情報を発信しています。新聞とPDF電子版は月3回の発行、WEBとTwitterは随時更新しています。